Last week, I gave a keynote at the RAPIDO workshop, part of the HiPEAC 2026 conference taking place in Kraków, Poland. HiPEAC is a computer architecture conference with a rather wild-grown set of simultaneous workshops in addition to a main-stage paper program. It is an event for presenting research, EU projects, and for companies to recruit highly qualified people. I had a rather interesting time getting to the conference, a story told in a separate blog post.

The conference was held in the very modern ICE Kraków Congress Centre. The main halls were clearly also used for concerts, and the sound dampening and acoustics were very impressive.

Kraków is well-known for its beautiful old town and castle, but honestly this time of the year it is not at its best. It was around freezing and quite foggy (which also impacted my travel to the event).

Conference Themes

The topic of the conference is computer architecture, in particular for high-performance compute. There is also quite a bit of embedded work, including very low-power compute. As already mentioned, there was a paper track that contained papers accepted to the ACM Transactions on Architecture and Code Optimization (TACO). The rest of the technical content was split into a large number of full-day and half-day workshops covering a very diverse set of topics related to computer architecture.

RISC-V was incredibly pervasive. It looks like anyone doing any kind of architecture research, regardless of whether it is a microcontroller, general-purpose processor core, or accelerator is using RISC-V as their base instruction set. This covers both custom cores and

Given that HiPEAC itself is an EU project, it is not surprising that there were many presentation of EU projects. Not just results from EU projects, but also the projects themselves.

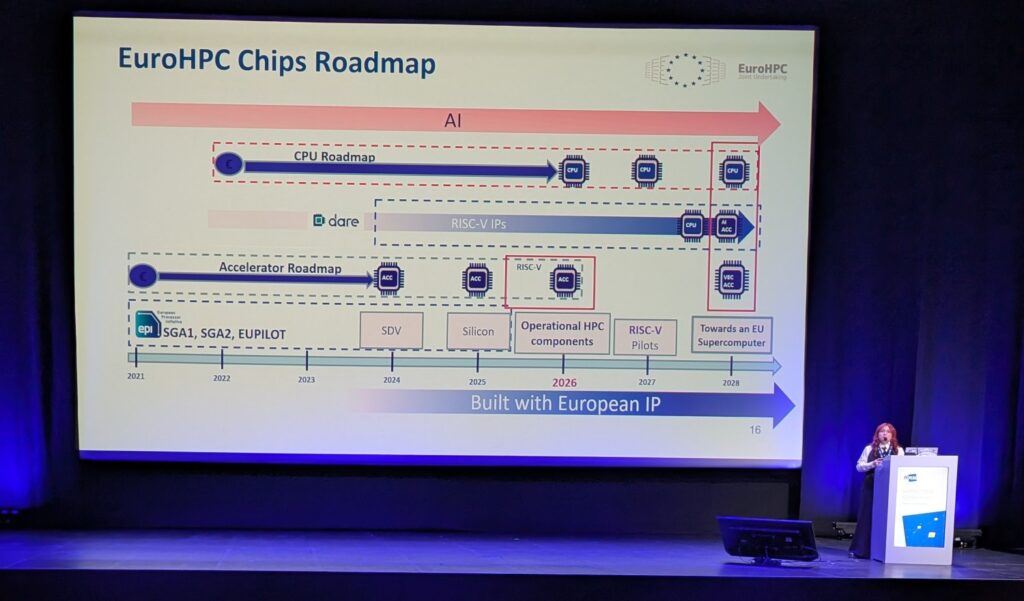

Combining EU and RISC-V, there was a session dedicated to RISC-V as the basis for high-performance computing for Europe. The EU has been providing rather generous funding (for the EU at least) for projects that aim to build leading-edge processors on leading-edge processes using leading-edge chiplet technology. The projects have started with various accelerators but are also trying to find a way to get RISC-V-based true high-performance cores designed in Europe. That last part is critical, but it does look like it is quite there yet.

AI Keynote

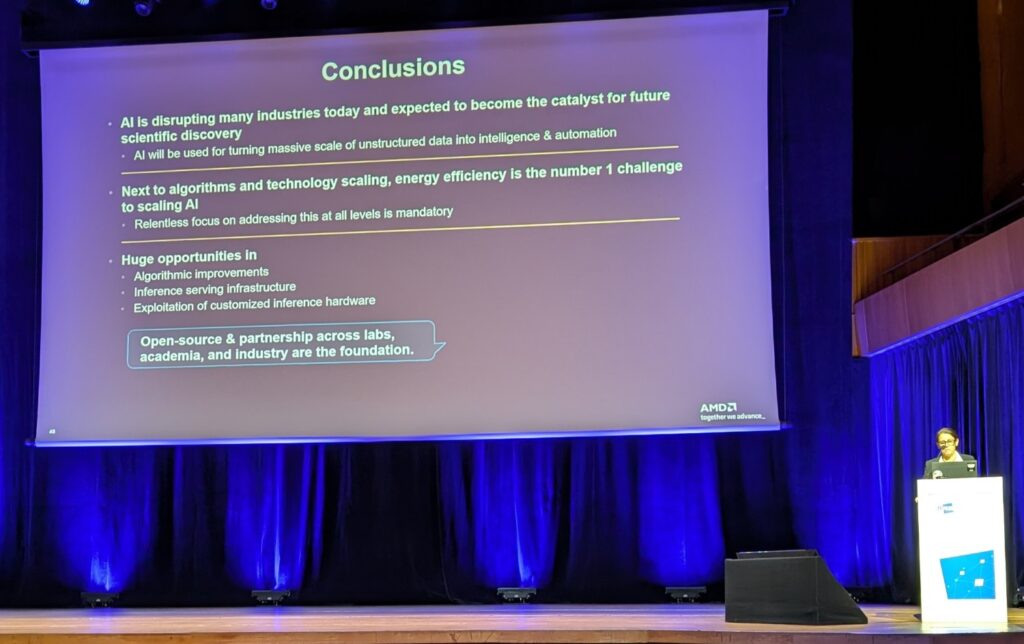

The first day’s keynote was given by Michaela Blott from AMD in Ireland. Kind of funny, this is the third time I have heard her give keynotes. First at DVCon Europe in 2023, then DAC in 2025, and now HiPEAC in 2026. As always, it was about what is going on in AI (mostly, LLMs, but also other forms of machine learning and deep neural networks) and the need to make AI inference much more energy efficient. As time goes on, more and more emphasis is being placed on efficiency and a huge variety of techniques are being tried to allow LLMs to produce good results at drastically reduced power.

NextCloud Keynote

Frank Karlitschek gave the second keynote. He is a long-term open-source advocate and a founder of the NextCloud project. This was a very different type of talk, discussing how Europe can and should break its dependence on US cloud platforms. It is not easy to do, but NextCloud offers a technology platform that lets you build systems approximating both productivity systems like Microsoft 365 and social media and chat systems.

I particularly liked the way he used email as an example of how you should build communications systems. Build a standard and let everyone run their own servers, with no central entity needed. Using the right protocols, we can build federated systems where you own your own data and selectively let other people access it via explicit sharing. No central entity needed. Just like email, a little more work, but the result is a lot more “data sovereign”.

RAPIDO Keynote

I gave a keynote presentation at the RAPIDO workshop about virtual platforms for architecture, software development, and long-term software maintenance. I presented it based on the “Banana Model”:

Basically, this is a super-simplified V model, extended with the aspect of long-term software maintenance. To emphasize the theme, I also gave out some simulated candy bananas.

Exhibition

The exhibition was clearly focused on recruiting, with a rather broad set of companies represented.

Arm was a major sponsor of the conference and obviously out to recruit computer architecture talent. They also presented their academic program where you can get access to many Arm IP blocks to build complete ASICs in a way that is very similar to what happens in industry!

The best on-brand give-away was from ASML. They leaned into being a Dutch company by giving away branded bicycle lights. Just love it.

AMD had a nicely color-coordinated booth, if you consider black a color. They were both recruiting people and information about their academic offering. The coffee mugs were very nicely designed too.

The Barcelona Zettascale Labs showed off several actual working chips in their booth. All of them I believe were RISC-V based, and the manufactured on some rather aggressive nodes. In particular, one chip was manufactured by Intel in Ireland on the Intel3 process.

Recalling the Start of HiPEAC

I had kind of forgotten about it, but I was part of starting the HiPEAC conference way back in the days in 2005 when I was still a part-time professor at Uppsala University while working at Virtutech with the Simics simulator. The story was documented by Matteo Valero in an article in HiPEAC Info #74. Written in 2025, when HiPEAC celebrated its 20th anniversary.

The article tells the story of the start of HiPEAC, as it grew out of European embedded research, aiming towards high-performance computing. It was a prescient vision, considering that we today talk about “HPC” as a primary type of compute node in car networks (central compute for SDV). Of course, the research presented in 2026 is not just about embedded, but also about computer architecture for everything up to supercomputers and AI factories.

Seeing my own name along a long list of far better known professors and industry luminaries is fun.